- Synplify pro tutorial verification#

- Synplify pro tutorial software#

- Synplify pro tutorial Pc#

- Synplify pro tutorial license#

Synplify pro tutorial software#

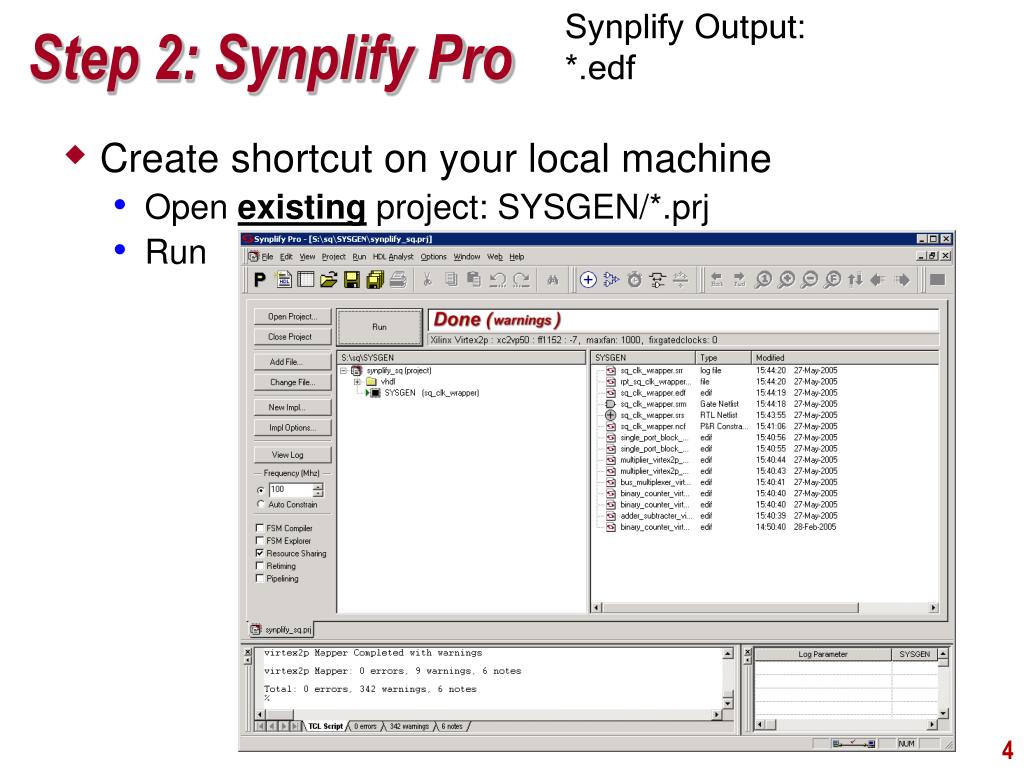

These very updates must then be reflected quickly in a new revision of the prototype.Ĭertify and Synplify Premier software can read and synthesize FPGA prototypes from ASIC RTL that references DesignWare Library IP.

Synplify pro tutorial verification#

This is particularly desirable because FPGA-based verification typically proceeds based on snapshots of the design, where updates to the source are expected to occur frequently as the design evolves. The ability to synthesize FPGA-based prototypes from the same RTL design source that references these DesignWare components is key to allowing both the ASIC hardware team and the FPGA verification team to operate from the same synchronized set of RTL source files and IP.

Today, many ASIC hardware designs reference DesignWare Library IP in their RTL to gain higher ASIC QoR and greater productivity through the abstraction and ASIC optimizations available for these components. These prototypes also form a software development platform, enabling the system software team to test and integrate applications that will eventually run on the ASIC design. With the cost of a mistake in a tape out of an ASIC design being so high, and with system design cycles being so long, designers are turning to FPGA-based prototyping to perform at-speed or close to at-speed validation of their ASIC design prior to tape out. The risk associated with the first two tasks of compliance testing and controller/PHY interoperability is significantly reduced when using the DesignWare cores with Synopsys’ HAPS® prototyping motherboards, since these tasks have already been performed before by Synopsys.Īn example of the use of a DesignWare USB 3.0 core with the HAPS FPGA-based Prototyping Solution is shown in Figure 6.

Synplify pro tutorial Pc#

Note that the DesignWare Building Blocks IP installation must occur on a Linux or Solaris machine, but this IP library can subsequently be accessed for FPGA synthesis by Synplify Premier and Certify software on a PC running Windows or Linux. It is also recommended that you set the following to ensure that the tool is accessing the DesignWare Building Blocks and not a legacy library: set_option -enable_DesignWare 0

Synplify pro tutorial license#

0 kommentar(er)

0 kommentar(er)